算术运算单元ALU的设计与实现

算术运算单元ALU的设计与实现

这是2018年大三时的一个课程设计,在这里把相关技术和用到的知识分享给大家。(由于编者水平有限可能存在错误的地方,欢迎大家指正)题目给出的要求如下:

一、设计题目及要求

要求:

1.进行两个四位二进制数的运算。

2.算术运算:A+B,A-B,A+1,A-1

3.逻辑运算:A and B,A or B,A not, A xor B

注意:从整体考虑设计方案,优化资源的利用

二、设计过程及内容

2.1总体设计

ALU算术运算单元由以下几个部分构成:

图1 ALU运算单元系统结构图

为了尽可能减少资源的使用(或以相同的资源增加更多的功能),在此系统的基础上,增加基于寄存器的分时复用输入模块进行改进。

图2 基于分时复用方法的ALU运算单元结构

①输入模块

该模块用于两个四位二进制数的输入。通过使用实验箱的拨码开关,输入高低电平,表示二进制的 1和0,四组拨码开关组合可以表示一个四位二进制数。

②逻辑运算单元

该模块用于两个四位二级制数的逻辑运算。通过列出一位二进制数逻辑运算的真值表(含有四种不同的逻辑运算功能),得出了一位二进制数逻辑运算单元的表达式(已使用卡诺图化简)。将按照逻辑表达式连接好的多个一位二进制逻辑运算单元进行组合,可得到多位二进制数逻辑运算单元。

通过使用“真值表+卡诺图”的方法将所有的逻辑运算的表达式融合在一起进行化简,可以最大化减少使用门电路的数量。使用子模块组合的方式可将逻辑运算单元由一位扩展到多位,进而增加了模块的可扩充性。

图3 逻辑运算单元结构示意图

③算术运算单元

该模块用于计算两个四位二进制数的加减法运算。使用4位超前加法器74283实现加法功能。根据计算机组成原理的相关知识,减法可以视为补码的加法运算,即A-B=A+B_补=A+B_反+1,因此在实现加法运算的基础上进行改进,可以得到所有的算术运算功能。

该模块的实现过程为,使用2个功能控制线对输入的4个经过不同处理的B数据进行选择(不同处理包括原码输入、对输入的原码取补码、直接视为1、直接视为-1的补码),通过一个74283加法器,输出计算结果。

④功能控制模块

该模块实现了对运算类型的选择。通过对一根功能选择线置不同的电平实现了算术运算功能和逻辑运算功能的选择。从系统的角度来看,功能选择线有三个,F_3 F_2 F_1,F_3实现了运算类型选择,F_2 F_1实现了对每种运算类型4种不同功能的选择,具体分类见表1。

⑤补码-原码转换模块

将四位二进制数的补码转换为原码。根据算术运算单元的原理,可知该单元是将结果以补码形式输出的,考虑到负数的补码不便于观察结果,因此设计该模块的目的是将算术运算的结果转换为原码并将符号位输出,通过显示模块以原码形式显示,从而使运算结果可以直观观察。

⑥显示模块

该模块用于显示系统的运算结果。根据该系统以二进制码的形式输出结果的特点,选择LED灯作为显示装置,进而可以直观的显示运算结果。选择6个LED灯,第一个灯显示符号位,第二个灯显示进位信号,其余四个灯为运算结果的原码显示。

图4 显示装置示意图

显示进位端的目的是为了防止算术运算溢出的发生。对于两个正数相加而言,最大值为1111+1111=11110,共5位;对于两个四位二进制数做差而言,最小值为0000-1111=-1111,共4位。

在实际设计中,为了减少资源的利用,取消符号位的Sign的LED灯,将负数显示用Co来表示。当进行做差运算时,Co亮表示结果为负数;当求和运算时,Co表示进位信号。

2.2使用分时复用方法改进后的系统

对系统进行改进的目的是为了尽可能减少资源的使用。对比计算机体系结构中,采用分时复用方式向内存发送地址,进而减少管脚数的方法,设计了基于JK触发器的寄存器分时复用输入模块,改进后的系统总图和分时复用输入模块结构图如下所示:

图5基于JK触发器的寄存器分时复用输入模块结构

通过使用分时复用方法,可将原来的8个数据输入端减少为4个数据输入端,但增加了1个时钟信号输入端和一个寄存器转换端。时钟信号输入端与拨码开关相连接,用户通过拨动开关,产生脉冲,由于JK触发器是上升沿触发的,进而可以存储数据。

同时,对总系统增加了Oper控制端,可以将显示模块的内容从运算结果转换为寄存器中的内容,即寄存器中的内容可以通过控制Oper端进行显示,对用户可见。

2.3各模块的结构设计及仿真

该部分将对各个模块的设计方法加以说明,并给出由QuartusII对模块进行的仿真结果,并加以说明。该部分分为a.逻辑运算单元、b.算术运算单元、c.数据选择模块、d.分时复用输入模块以及e.显示模块五个部分。

a.逻辑运算单元

按照图2所设计的结构,首先对一位二进制数逻辑运算单元进行了设计。

(1)真值表

(4)4位二进制逻辑运算单元模块

图7 四位二进制逻辑运算单元结构

采用并联的方式,将C1,C2与一位二进制逻辑运算单元相连接。

(5)功能仿真(用以验证模块的正确性)

由于逻辑模块功能较多,这里只给出了部分结果,详细结果见附录2

5.1and功能仿真

5.2or功能仿真

图9 or功能仿真图

从仿真结果中可以验证模块设计的正确性,从而可以进行时序仿真。

(6)时序仿真

6.1not时序仿真

图10 not时序仿真

6.2xor时序仿真

图11 xor时序仿真

由于竞争冒险现象的存在,使得时序仿真出现了不少毛刺,但这些毛刺对没有边沿触发器的逻辑运算单元没有影响,仿真结果均符合实际情况,因此该单元可以作为系统的子模块。

b.算术运算单元

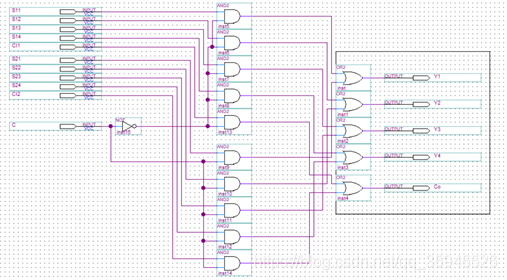

图12 算术运算单元总图

根据前文所述,通过F和C实现对数据B进行4中不同处理后的得到的结果进行选择。从结构图中可以看出

当F=0时,实现的是加法运算,数据B中的每一位与0异或结果不变,得到的还是B,74283的进位端CI输入也为0;非门方框产生的数据为0001,;这两个数据,通过C=0或C=1控制Control2模块进行数据选择,从而实现了A+B、A+1的功能。

当F=1是,实现的是减法运算,两个方框将减数转换成补码。对于XOR方框,B的每一位与1异或,得到的是B^’,74283的进位端为1;NOT方框输入的值为0111;根据B_补=B_反+1的关系,这两个数据与进位端的1相加,得到的两个数据为B_补和〖-1〗_补,通过C=0或C=1控制Control2模块进行数据选择,从而实现了A-B、A-1的功能。

进位信号在减法的情况下可以视为运算结果的符号位(减法情况下不可能由进位),结合计算机组成原理的相关知识,由

D_补=2-D_原(D_原为不大于2的二进制数,大于2同理) 式1-2

可得

A-D=A+2-D_原 式1-3

当A>D时,会产生进位信号,此时运算结果为正数,此时符号位应为0;

当A<D时,2被负数抵消一部分,此时不会产生进位信号,运算结果为负数的补码,此时符号位应为1。

通过上述分析,选取进位信号与功能选通端F取异或,可将进位端变为符号位。![在这里插入图片描述]

1.功能仿真(验证模块的正确性)

由于仿真图较多,这里将采取随机功的方式对所有功能进行仿真

图13逻辑运算单元的功能仿真图

从图中可以验证结果的正确性。当CF=00是实现的是A+B,第一条数据1010+0111=10001可以说明加法功能的正确性,后面的各条数据都能验证结果的正确性,这里不一一列举。

2.时序仿真

图14 逻辑运算单元的时序仿真图

时序仿真符合实际情况,竞争冒险现象不会对该模块产生影响,因此该模块可以作为系统子模块。

c.数据选择模块

图15 数据选择模块结构图

该模块由与门和或门电路组成。用于数据选择,当C=0时,实现对数据S1的选择,当C=1时,实现对数据S2的选择。该模块较简单,直接给出仿真图

图16 数据选择模块功能仿真图

图17数据选择模块时序仿真图

通过该模块的仿真图可以验证模块设计的正确性,时序仿真图说明了竞争冒险现象不会影响最终结果,因此该模块可以用作系统子模块。

d.基于JK触发器的寄存器分时复用模块设计

图18 分时复用模块结构图

该模块采用了8个JK触发器用于数据寄存,8个触发器分成2组,每4个触发器一组(形成一个数据寄存器),用于记录一个4位二进制数据。当C=1时,寄存器2的输入端为0,JK触发器处于保持状态,进而实现了对寄存器1的数据写入,同理实现对寄存器2的数据写入。

CLK与实验箱的拨码开关连接,当拨码开关从低电平拨到高电平时,产生一个上升沿信号,实现JK触发器对数据的写入。

1.功能仿真(验证结果的正确性)

图19分时复用模块的功能仿真图

2.时序仿真图

图20分时复用模块的时序仿真图

CLK采用随机信号产生上升沿,S1out表示寄存器1中的内容,S2out表示寄存器2中的内容。开始时C为1表示对寄存器1中的数据进行输入,当上升沿未来到前,寄存器中的内容为0000,当上升沿来到后寄存器对Input的输入数据进行了存储,变为了1011,下一个上升沿来临前,C变为了0,实现对寄存器2中的数据进行写入,当上升沿来临后,经Input中的数据写入到寄存器2中,以此类推可以验证逻辑的正确性。

从时序仿真图中,可以发现,其结果与功能仿真得到的结果相同,竞争冒险现象不会影响模块的实际输出,因此该模块可以作为系统的子模块。

e.补码-原码转换模块

图21 补码原码转换模块结构图

该模块由74283超前加法器和数据选择模块构成,从结构图中可以看到,输入数据分成了两路,第一路作为数据选择模块的S1进行输入;第二路通过取反将数据置入74283超前加法器(进位端置1)取补码,作为数据选择模块S2的输入,该原理是根据〖D_补〗_补=D_原的关系实现的。

对于两路数据的选择,通过Control2的功能控制端C来确定。对实际情况进行分析,仅有当减法的情况下,才可能出现负数补码的情况,通过查阅操作码表可知,此时F_3=0,F_1=1;

根据上述分析,当为减法运算时,进位端输出的是符号位,可以得到Control2的功能控制端的逻辑表达式为

C=C_i C_1 C_2^’ 式1-4

1.功能仿真

图22 补码-原码转换模块功能仿真图

2.时序仿真

图23 补码-原码转换模块时序仿真图

通过功能仿真可以验证电路设计的正确性,当C1,C2为0,1,C0=1时,表示减法功能产生的负数补码,因此对其进行转换;转换完毕后C0恢复,继续表示进位信号,使用新增加的Sign输出符号位。时序仿真结果与功能仿真一致,说明竞争冒险现象不会对电路产生影响,因此该模块可以作为系统的子模块。

f.系统总模块的设计与仿真

将上述各个模块进行组合,可以得到图2所示的基于分时复用方法的ALU运算单元,由于该系统考虑到了不同的时间通过控制拨码开关将不同的值输入到不同的寄存器,从总体的仿真图来看,控制变量众多,难以进行分析验证。

将系统分为两个可连接的模块分别进行仿真,第一个模块的输入等于第二个模块的输入。只要仿真结果正确,即可证明系统设计的正确性。

根据ALU运算单元的特点,将系统分为分时复用输入模块+运算单元两部分进行考虑。

图24 数据输入模式

结合d的仿真结果,只需要对图24(即图1)所示的运算单元进行仿真即可。

图24 ALU运算单元系统结构图

1.功能仿真

图25 ALU运算单元功能仿真图

2.时序仿真

图26ALU运算单元时序仿真图

对照表1所示的功能码,结合实际结果,对功能仿真的结果进行验证,可以得到运算结果均正确的结论。由图26可知,竞争冒险现象不会影响系统功能,因此,该系统可以正常工作。

完

推荐阅读